정규논문 (Regular Paper)

방송공학회논문지 제19권 제5호, 2014년 9월 (JBE Vol. 19, No. 5, September 2014)

<http://dx.doi.org/10.5909/JBE.2014.19.5.726>

ISSN 2287-9137 (Online) ISSN 1226-7953 (Print)

## UHD급 영상패턴 제어 신호발생기를 위한 고속 시리얼 인터페이스의 신호 무결성 분석

손희배<sup>a)\*</sup>, 권오근<sup>a)</sup>

### Analysis of Signal Integrity of High Speed Serial Interface for Ultra High Definition Video Pattern Control Signal Generator

Hui-Bae Son<sup>a)\*</sup> and Oh-Keun Kweon<sup>a)</sup>

#### 요약

최근 초고화질(UHD) 영상시스템의 출현으로 인해 고해상도, 대용량의 4K-UHD급 LCD TV 신호 전송은 높은 해상도와 데이터 확장에 따른 케이블 및 커넥터 수의 증가로 서로 다른 케이블 간의 EMI, 스큐(Skew) 문제로 시스템 구현에 한계가 있다. 차세대 V-by-One HS 인터페이스는 초고해상도 영상처리 IC 및 TCON 간의 새로운 인터페이스 기술로써 600Mbps에서 3.75Gbps의 다양한 데이터 속도로 효율적인 전송이 가능하여 한계를 극복할 수 있다. 본 논문에서는 V-by-One HS IBIS(Input/ Output Buffer Information Specification) 모델 시뮬레이션을 통하여 주파수 공진모드의 전압 분포와 PCB 설계 방법을 제안하고 고속영상 신호에 대한 신호 무결성의 검증 방법을 제안하였다.

#### Abstract

In accordance with 4K UHD(Ultra High Definition) LCD television's higher resolution and data expansion, LCD TV had to face problems such as increasing numbers of cables and tangible skews problems among cables. The V-by-One HS is a new interface technology in the path between the image processing IC and timing control (TCON) board. The variable speed from 600 Mbps to 3.75 Gbps effectively meets the requirements of various different pixel rates. In this paper, we use the V-by-One HS interface to illustrate our proposed simulation method of frequency resonance mode and PCB design approach to model the effects of signal integrity for high speed video signal using an IBIS models.

Keyword : Ultra high definition, Video generator, High speed signal, Video interface, Signal integrity

#### I. 서론

a) (주)엠아이케이21 (MIK21 CO., LTD.)

\* Corresponding Author : 손희배 (Hui-Bae Son)

E-mail: mrson@mik21.com

Tel: +82-55-256-7817

※ 본 연구는 우수제조기술연구센터(ATC)사업으로부터 지원 받아 수행 되었습니다. (10032935)

· Manuscript received August 1, 2014 Revised September 4, 2014

Accepted September 11, 2014

차세대 방송 서비스는 디지털 기술의 발전으로 디스플레이 장치들은 단순한 출력 장치의 기능 이상으로 다양한 멀티미디어 콘텐츠 정보를 고품질의 영상 정보로 변환하여 사용자에게 전달하는 매개체 역할을 하고 있다. HD급

영상에서 UHD(Ultra High Definition)급 영상으로 고품질 실감 방송 서비스로 발전되고 있으며, UHD 디지털 TV 방송은 HDTV 방송의 4배 해상도(3840x2400)를 가진 4K2K-UHDTV와 16배의 해상도를 가진 8K4K-UHDTV의 디스플레이 및 방송기술이 개발되고 있다<sup>[1-3]</sup>. 또한 UHD급 멀티미디어 콘텐츠 종류의 증가와 고해상도의 다양한 정보 전달을 위해 표현해야 되는 정보량이 증가하고 이러한 정보를 효율적으로 표현하기 위하여 대면적, 고해상도의 디스플레이 장치가 요구되어 디스플레이 시스템 내부에서 처리해야 하는 정보량이 증가하고 있다<sup>[4-6]</sup>. 따라서 UHD급 고해상도 디스플레이 시스템 내에서 신호의 무결성을 보장하면서 고속으로 신호를 전송하는 고속 인터페이스 기술이 평판 디스플레이 구동회로 분야에 있어 매우 중요한 기술 중 하나가 되었다<sup>[7]</sup>. 고해상도의 영상신호 정보를 효율적으로 표현하기 위하여 디스플레이 시스템 내부에서 고속 영상신호 전송을 해야 하며 기존의 디스플레이 인터페이스 전송방식인 LVDS(Low Voltage Differential Signaling)로 고속의 대용량 데이터를 전송하면 데이터 지연에 따른 스케ю(Skew) 현상 및 EMI 문제가 발생하여 기술적인 한계가 있다<sup>[8-10]</sup>. 특히 UHD급 해상도(4K2K) 이상의 디스플레이 시스템을 구현하기 위하여 디스플레이 내부에 TCON(timing control) 간의 새로운 인터페이스 기술이 요구되어 진다<sup>[11-13]</sup>. HD급 해상도 인터페이스에서 사용되는 LVDS 신호 전송은 UHD급 디스플레이 장치를 구동하기 위하여 LVDS 전송선 수를 증가시켜 동작 시켰으나 케이블 수의 증가로 인한 EMI 발생 및 기기 내의 공간 부족 등의 이유로 UHD급 고속 데이터 전송 인터페이스인 V-by-One HS 방법이 제시 되었다<sup>[14]</sup>. V-by-One HS 전송 방법은 LCD 패널 내부 영상처리 PCB 보드와 TCON 보드 간의 새로운 인터페이스 기술로 THine Electronics사로부터 사양이 공개표준화 되어있다<sup>[15]</sup>. 이 전송 방법은 기가비트 시리얼 인터페이스 전송기술로 SerDes(Serializer/ Deserializer)로 최대 40bit/화소의 데이터를 1 레인(lane) HSD(High Speed Differential) 신호로 전송하며 클록 데이터 복구에 의한 전송선로 간 스케ю문제를 줄여 EMI를 감소시켜 우수성이 제시<sup>[11-15]</sup>되고 있으나 고속 영상신호 전송에 따른 고주파 전송선로에서 신호 무결성(signal integrity) 특성의 분석이 요구된다.

본 논문에서는 V-by-One HS 신호를 이용하여 UHD급 영상패턴 제어 신호발생기를 구현하고 HSD 전송선로 인터페이스에 대하여 신호 무결성을 검증하고자 한다.

## II. UHD급 영상신호 인터페이스

### 1. 디스플레이 인터페이스

디스플레이 인터페이스는 영상장치들의 디스플레이 패널과 영상신호를 제어하는 IC 사이의 데이터 송수신에 사용된다. 이러한 데이터 송수신에서는 LVDS 기술 표준을 많이 사용하였으나 최근 영상신호 데이터의 대용량, 고속화 되면서 전송선 수의 증가로 인한 공간부족 및 비용증가로 UHD급 영상신호 전송에 한계가 있다. 이러한 LVDS의 한계를 극복하기 위해 다른 여러 가지 표준들이 등장하게 되었으며 본 논문에서 제안하는 UHD급 영상신호 인터페이스 표준인 V-by-One HS를 사용하여 고속 영상신호 인터페이스에 대하여 다룬다.

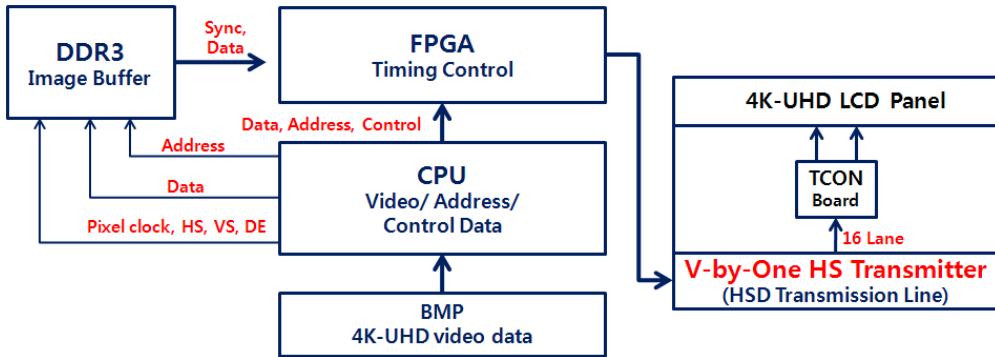

V-by-One HS는 LVDS에 비해 증가된 대역폭을 가지고 클록 데이터 스케ю를 제거하기 위하여 CDR(Clock Data Recovery)이 포함된 클록을 사용한다. 데이터 전송속도가 600Mbps에서 3.75Gbps로서 가변적으로 동작하고 소비전력을 감소시킨다. THine사의 독창적인 이퀄라이저 기술은 높은 영상품질과 LVDS보다 적은 수의 케이블 및 커넥터 사용함으로서 원가 절감이 가능하다<sup>[10-15]</sup>. 그림 1은 UHD급 영상신호 인터페이스 구성도이다. 4K-UHD급 영상신호를 구현하기 위하여 LCD 패널에 고해상도의 V-by-One HS 영상 데이터가 입력되어야 한다. 4K-UHD급 BMP(bit map) 데이터를 사용하여 영상을 입력하고 임베디드 CPU에서 RGB 10bit 데이터 및 어드레스, 동기 신호를 DDR3 메모리에 전송한다. FPGA는 UHD급 영상신호의 H sync, V sync, ED, Dot 클록 신호를 V-by-One HS 입력신호에 맞게 데이터 RGB 16 레인(lane)으로 구현한다. 입력된 UHD급 V-by-One HS 영상신호는 TCON 보드를 통하여 4K-UHD LCD 패널로 고해상도 영상신호가 디스플레이 된다.

그림 1. UHD급 영상신호 인터페이스 구성도

Fig. 1. Block diagram of Ultra-HD video signal interface

## 2. UHD급 고속 영상신호 전송

고주파 전송선로의 설계는 일반적으로 다층구조(multi layer)로 설계되며, 이러한 구조는 고속 영상전송에서 나타날 수 있는 잡음, 지터 및 EMI 복사현상을 억제시키기 위하여 다층기판의 치수, PCB의 두께와 재질에 따라 결정되므로 고속 전송에 따른 신호 무결성(signal integrity) 특성과 전원 무결성(power integrity) 분석을 해야 한다. 다층구조의 PCB(printed circuit board) 설계에서 고려되어야 할 사항은 전기적 EMI 문제를 해결하기 위한 다접지(multi-point ground)방법이며 이에 따른 임피던스 결합(impedance coupling)이다. 이러한 문제점을 해결하기 위하여 AC 결합 커플러를 적용하거나 RF 쇼크(chock)를 사용하여 임피던스의 결합관계를 해결해야 한다. 고속 전송선로에서 전자기적 문제의 발생 요인은 다층기판의 환경적 요소에 의한 임피던스 변동은 신호 무결성과 함께 임피던스 변화에 따른 전원공급이 전압의 변동에 의한 전원 무결성 현상을 억제시켜야한다. 전원 무결성은 고속 전송선로에서 비아-홀(via-hole)의 설계에 의하여 억제시킨다<sup>[8]</sup>.

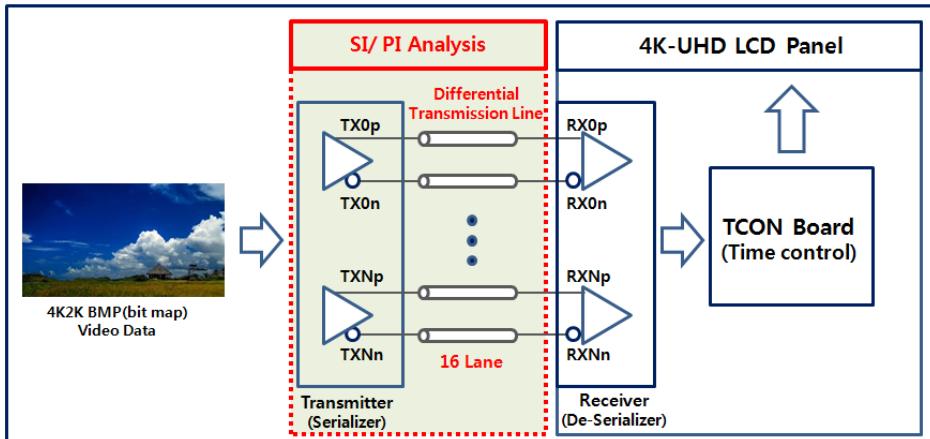

그림 2는 4K-UHD 영상전송을 하기위한 16 레인의 HSD (High Speed Differential) 전송선로 및 V-by-One HS 직렬 변환기(Serializer/ Deserializer) 시스템 구성도이다. 4K-UHD급 BMP 영상 데이터를 영상처리 하여 직렬 변환기 시스템에 의해 4K-UHD LCD 패널에 전송되며 이때 전송

그림 2. 4K-UHD급 고해상도 영상신호 전송 시스템 구성도

Fig. 2. Block diagram of 4K-UHD high definition video signal transmission system

선로의 신호 무결성(SI), 전원 무결성(PI)의 특성에 따라 고속 영상신호의 품질에 영향을 받는다. 이와 같이 4K2K 고해상도 영상신호를 디지털 TV 패널에 전송시키기 위하여 고주파 전송기법에 의한 PCB를 설계하고 고속 영상전송에 따른 신호 왜곡 및 지터 등 신호 품질에 대한 분석이 요구되어진다.

### III. UHD급 영상신호 인터페이스 전송선로

#### 1. 고속 영상신호 전송선로 분석

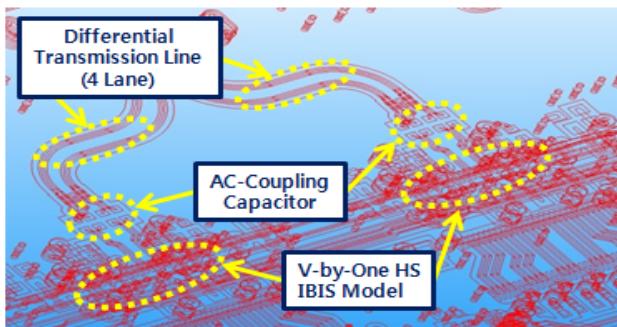

4K-UHD급 대형 패널 시스템 내부에서 고화질의 영상신호를 고속으로 전송하기 위하여 그림 3과 같이 영상패턴 제어 신호발생기의 내부 인터페이스 보드를 구성하였다.

그림 3. SIWAVE를 사용한 V-by-One HS 전송부

Fig. 3. V-by-One HS transmitter in SIWAVE

대형 패널 시스템 내의 TCON 보드와 V-by-One HS 전송선로 사이에 고주파 특성을 고려한 마이크로스트립 선로 (microstrip transmission line)를 설계하여 UHD 영상신호 왜곡을 제거 시켜야한다. 고주파 전송선로 기법에 의한 다층구조 PCB 설계는 V-by-One HS 고속 영상신호를 출력하기 위한 THine사의 SerDes THCV215 칩을 사용하여 IBIS(Input/ output Buffer Information Specification) 모델을 적용<sup>[5,6,8]</sup>하고 HSD 마이크로스트립 전송선로에 AC 커플링 커패시터를 구성하였다.

마이크로스트립 선로의 길이에 따른 Eye 패턴 특성을 분석하기 위하여 다층구조 PCB의 표면에 동일한 선폭을 가지는 HSD(high speed differential) 전송선로를 설계하였으며 PCB의 특성 임피던스는 마이크로스트립 전송선로의 길이, 패턴 두께 및 간격 등에 따라 신호의 특성이 결정 되어 HSD의 특성 임피던스는 다음 식과 같다.

$$Z_{diff} = \frac{174}{\sqrt{\epsilon_r + 1.41}} \ln\left(\frac{5.98h}{(0.8w+t)}\right) \left(1 - 0.48\exp\left(-0.96\frac{d}{h}\right)\right) \quad (1)$$

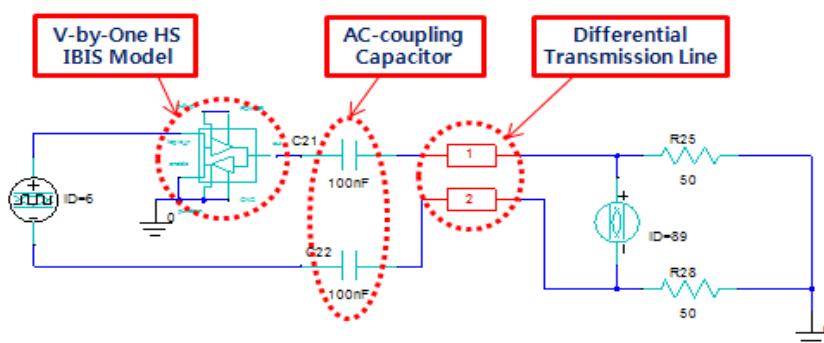

실제 구현한 HSD 전송선로의 특성 임피던스는 다층구조의 PCB 비유전율  $\epsilon_r=4.7$ , PCB 패턴 폭  $w=0.203$ , 패턴의 간격  $d=0.203$ , 베타층 위의 높이  $h=0.18$ , 패턴의 두께  $t=0.0175$ 에 의해 식 (1)을 계산하여 특성 임피던스가  $Z_{diff}=105\Omega$ 으로 설계되었다. 그림 4는 고속 회로 신호분석 Designer SI 프로그램을 이용하여 그림 3의 등가회로로 나

그림 4. V-by-One HS 전송단 설계(등가회로)

Fig. 4. DESIGNER model of V-by-One HS transmitter

타내었고 V-by-One HS의 전송칩 THCV215 IBIS 모델을 이용하여 회로에 적용하였다. HSD 전송선로에서 Eye패턴 소스에 2Gbps 신호를 입력하고 IBIS Core 공급전압을 1.8V, 마이크로스트립 선로의 길이는 실제 설계한 전송선로 길이를 고려하였다. V-by-One HS 인터페이스 영상신호의 마이크로스트립 전송선로는 수 Gbps 이상의 고속 데이터를 전송하므로 베타층을 그라운드 층으로 적용하여 신호 무결성에 대한 검증을 하고자 한다.

## 2. 고속 영상신호 인터페이스 보드 공진 특성

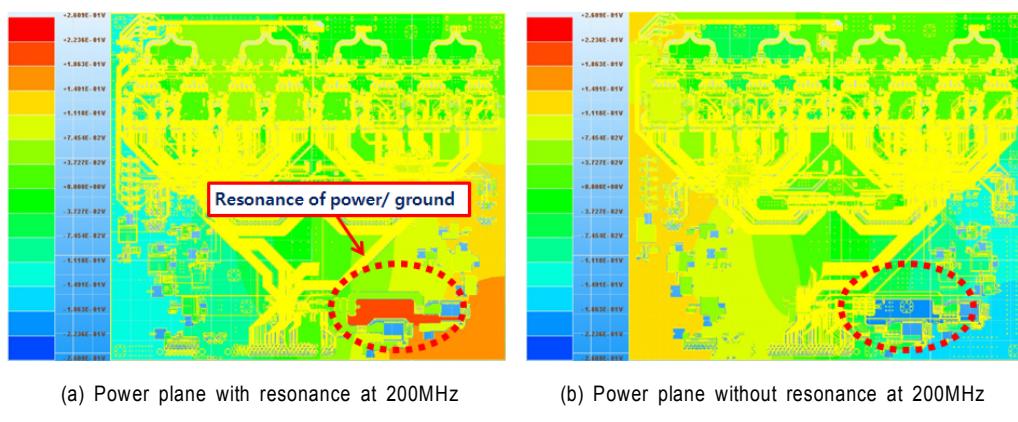

고속 영상신호 시스템에서 EMI특성은 특정 주파수대역의 신호가 전기적, 구조적으로 주파수가 일치될 때, 에너지가 집중되어 신호의 흐름을 방해하여 시스템이 불안정해지며 영상신호의 왜곡이 발생한다. PCB 설계에서 신호의 왜곡을 제거하기 위하여 EMI/ EMC에 대한 대책을 고려하여 PCB를 설계한다. 구현된 고해상도 인터페이스 보드에서 고주파로부터 전원층으로 유입되는 전자파 에너지가 V-by-One HS 전송선로에 영향을 억제하기 위하여 그림 5와 같이 설계한 다층기판에서 방사되는 EMI 노이즈를 분석한다. 다층기판에서 방사되는 EMI는 전원층(power plane/ ground plane)간의 전위차에 의해 발생하는 전계분포(E field)가 공중으로 방사하기 때문에 1GHz이하의 주파수 대역에서 EMI를 분석함으로써 고속 신호선로에 직접적으로

간섭이 일어나는 불필요한 공진(resonance)을 예측할 수 있으며 PCB 전반에 나타나는 EMI 노이즈 분포를 확인할 수 있다. 고주파 EMI 분석 프로그램(SIWAVE)을 사용하여 V-by-One HS 인터페이스의 다층기판에 전원층간 공진이 발생하는 전압분포를 나타내었으며 그림 5(a)에서와 같이 전원부의 EMI현상에 따른 불안정 원인인 공진을 제거하기 위하여 그림 5(b)에서 전원층과 그라운드면의 구조를 변경하고 비아 홀(via hole)을 추가 설치하고 전원부와 접지면 사이에 디커플링 커패시터를 배치한다. 실제 공진 주파수가 발생하는 V-by-One HS 인터페이스 보드에 공진특성을 재분석하고 공진특성의 최적화를 고려한 PCB를 설계하였다. V-by-One HS 인터페이스와 같은 고속 PCB 설계 시, 붉은 영역의 자기공진 주파수를 변환함으로서 자기공진 특성을 변경할 수 있고 신호의 무결성 및 특정 주파수 공진에 대한 PCB 검증에 적용할 수 있다.

## IV. 실험 및 분석 결과

### 1. 고속 영상신호 인터페이스 모의실험

설계한 마이크로스트립 선로의 다층구조 PCB는 8층으로 구성하였으며, 그림 3에서 설계한 V-by-One HS 인터페이스의 마이크로스트립 전송선로는 수 Gbps 이상의 고속

그림 5. SIWAVE를 이용한 주파수 공진

Fig. 5. Frequency resonance in SIWAVE

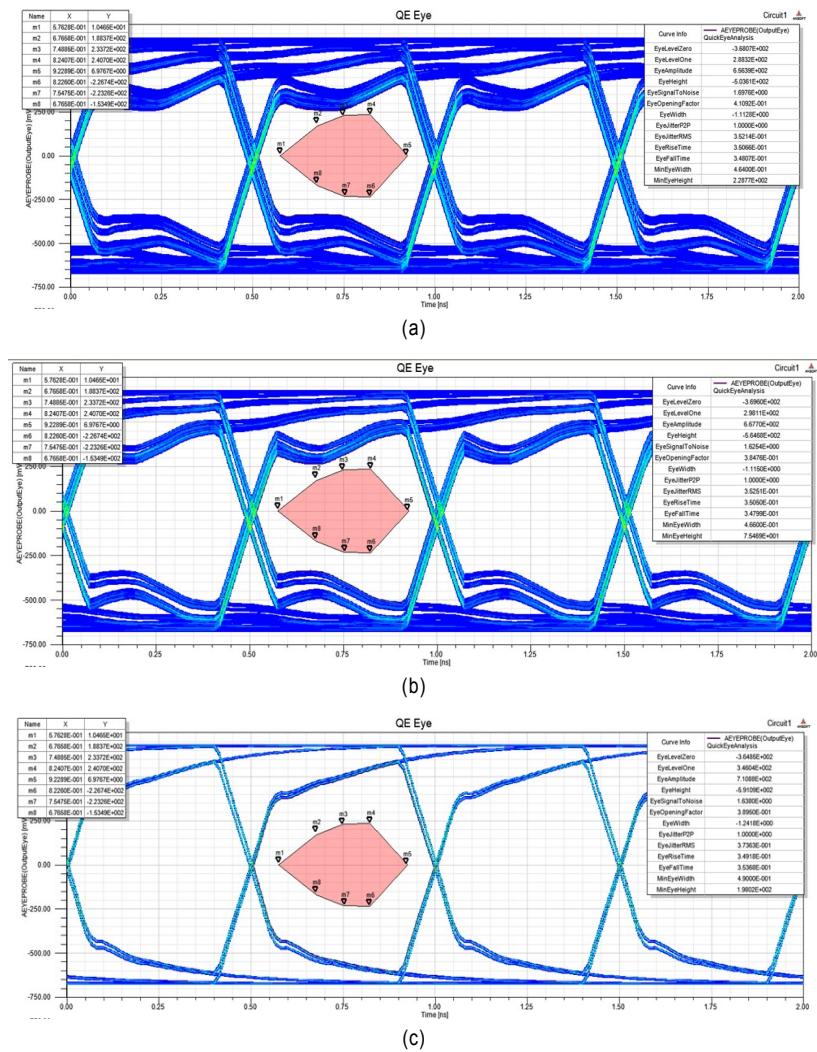

그림 6. 전송선로 길이에 따른 Eye패턴 분석 a) 200mm b) 100mm c) 50mm

Fig. 6. Eye pattern simulation according to transmission line length

데이터를 전송하므로 설계한 8층 기판구조에서 베타층을 그라운드로 하여 고속 영상전송 신호를 분석하였다. 송수 신단 사이에 전송되는 선로의 특성 임피던스는 PCB의 유전율 및 마이크로스트립 선로의 선폭과 선간 거리, 배선의 두께를 고려하여 100ohm으로 하였다. 그림 6은 실제 V-by-One HS 인터페이스 회로에 실제 적용된 IBIS 모델, AC 커플링, HSD 전송선로를 구성하고 고속 영상신호 출력의 특성을 분석한 Eye 패턴이다. 출력 신호를 분석하기 위하여 AC 커플링 커패시터를 100nF로 하여 설계한 HSD

전송선로에 길이의 변화를 그림 4의 등가회로에서 모의실험 하였다. 실험결과 전송선로 길이가 50mm, 100mm, 200mm 일 때, Eye 패턴의 변화를 확인 할 수 있었으며, 길이가 짧을수록 신호 대 잡음비 및 지터가 개선되었고 전송선로가 50mm이하 일 때, 고속 영상신호가 안정적으로 출력됨을 확인하였다.

표 1은 V-by-One HS 고속 영상신호 전송선로 길이 변화에 따른 Eye 패턴을 분석한 결과이다. 그림 6(c)에서 Eye패턴 크기가 710mV, 지터는 3.735ps, 상승/하강 시간은 각각

3.491/ 3.539(ps)로 영상출력 신호가 가장 안정적으로 동작함을 확인 하였다.

표 1. 전송선로 길이에 따른 Eye패턴 분석 결과

Table 1. Eye patterns simulation result according to transmission line length

| Eye Pattern Parameters | Eye Analysis |       |       |       |

|------------------------|--------------|-------|-------|-------|

|                        | 200mm        | 100mm | 50mm  | units |

| Level Zero             | -368         | -369  | -364  | mV    |

| Level One              | 288          | 298   | 346   | mV    |

| Amplitude              | 656          | 667   | 710   | mV    |

| Signal to Noise        | 1.697        | 1.625 | 1.638 | dB    |

| Jitter RMS             | 3.521        | 3.525 | 3.735 | ps    |

| Rise Time              | 3.506        | 3.505 | 3.491 | ps    |

| Fall Time              | 3.480        | 3.479 | 3.536 | ps    |

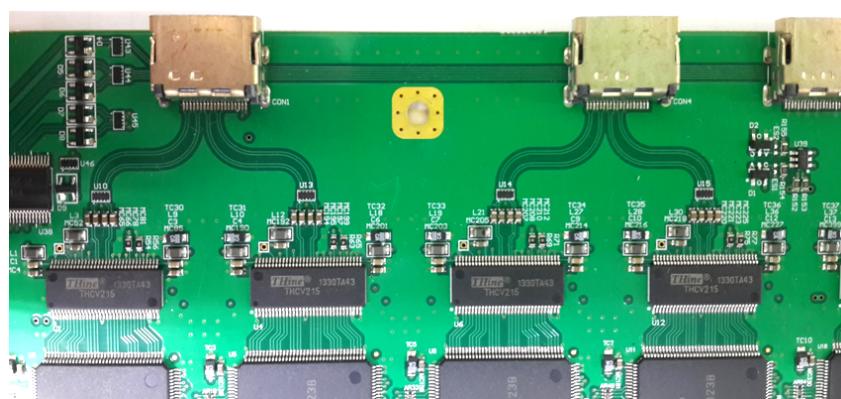

그림 7. 레이아웃과 배치가 좋지 않은 보드

Fig. 7. Layout was not good board

그림 8. 레이아웃과 배치가 개선된 보드

Fig. 8. The layout with the board where the placement is improved

## 2. 고속 영상신호 인터페이스 보드 분석

그림 7과 그림 8은 실제 제작된 실험보드 사진이다. 그림 3에서 제안한 트레이스 설계 방법으로 문제를 개선한 사례를 제시한다. 그림 3에서 제안한 것처럼 배선의 길이와 폭이 짧고, 배선의 길이를 고려한 부품의 배치가 설계해야 되는데 그림 7은 레이아웃과 배치가 좋지 않아 오동작을 일으킨 사례 사진이다. 그림 7의 보드에서 오동작의 원인이 되었던 주변 부품들의 배치 및 인더턴스의 길이와 폭이 그림 8에서 제안한 것처럼 짧고 부품들의 레이아웃을 대칭적으로 설계하여 개선된 것이다.

고속 영상신호 전송을 하기위하여 V-by-One HS 신호 출력단에 HDMI 커넥터를 사용하였으며 기존의 Centronics

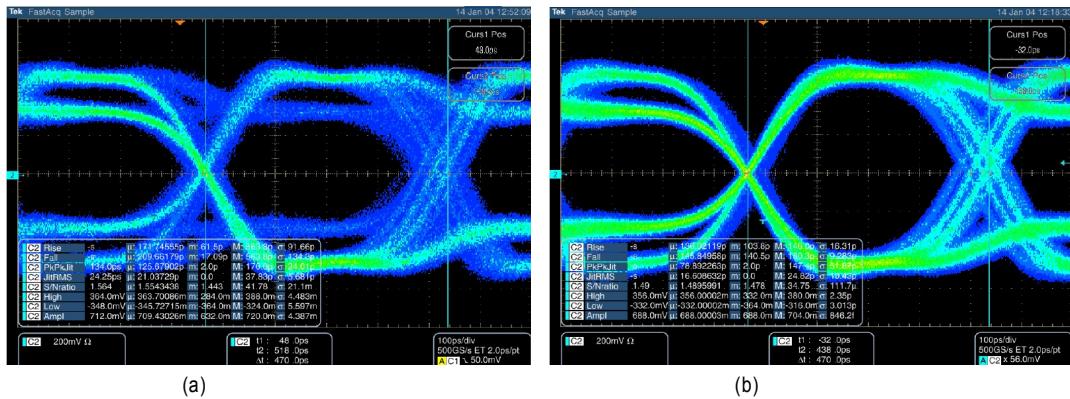

그림 9. 레이아웃과 배치에 따른 Eye패턴 측정 (a) 개선 전 보드 (b) 개선 후 보드

Fig. 9. Eye patterns measurement according to the layout and placement

타입 커넥터에서 HDMI 커넥터로 변경하면서 전송 케이블의 신뢰성이 확보되어 고속 영상 데이터 품질 및 전송길이

표 2. 제안한 보드의 Eye패턴 측정 결과

Table 2. Eye patterns measurement result of Proposed board

| Eye Pattern Parameters | Eye Analysis |          |       |

|------------------------|--------------|----------|-------|

|                        | before       | proposed | units |

| Level Zero             | -348         | -332     | mV    |

| Level One              | 364          | 356      | mV    |

| Amplitude              | 712          | 688      | mV    |

| Signal to Noise        | 1.55         | 1.49     | dB    |

| Jitter RMS             | 21.03        | 16.6     | ps    |

| Rise Time              | 171          | 136      | ps    |

| Fall Time              | 209          | 145      | ps    |

가 향상됨을 확인하였다. 그림 9는 V-by-One HS 인터페이스를 이용하여 4K2K@120Hz, 10bit, 2.13Gbps/ Lane의 초고해상도 영상패턴 제어 신호발생기의 영상출력 신호를 측정하였다. 표 2는 레이아웃과 배치가 개선된 전후의 Eye패턴 측정 결과이다. 표 2에서 개선된 보드의 Eye 패턴 출력 크기가 710mV, 지터가 16.6ps, 상승/ 하강 시간이 136/ 145(ps)로 전송 품질이 향상 되었다.

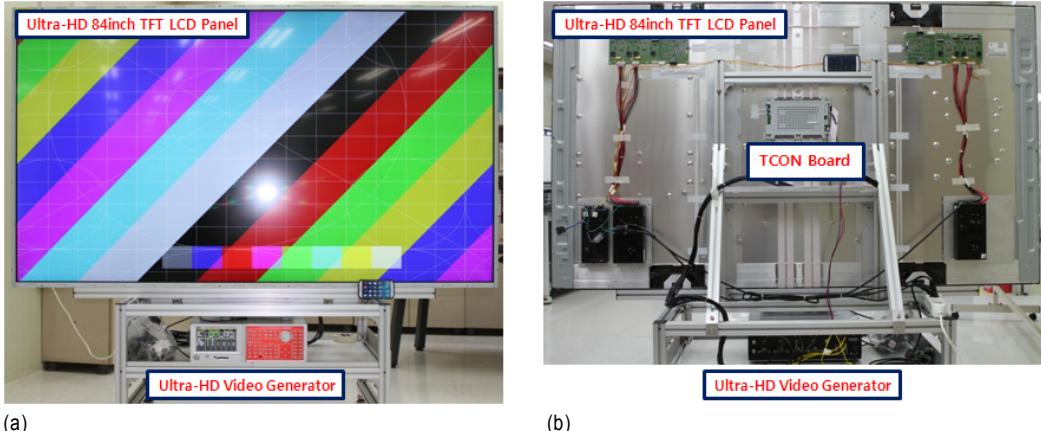

그림 10은 V-by-One HS 인터페이스를 이용한 실제 초고해상도 영상패턴을 디스플레이 하였다. 구현된 V-by-One HS 16레인 인터페이스는 84 인치 TFT LCD를 사용하여 3840\*2160@120Hz의 영상을 구현하였다.

그림 10. V-by-One HS 인터페이스를 이용한 UHD급 영상패턴 신호발생기 (a) Front view (b) Rear view

Fig. 10. Ultra high definition video pattern signal generator using V-by-One HS interface

## V. 결 론

본 논문에서는 V-by-One HS 인터페이스를 이용하여 초고해상도 영상패턴 제어 신호발생기를 구현하였고 Ultra-HD 디스플레이와 고속 시리얼 인터페이스 기술을 이용하여 대용량의 영상 데이터가 효율적으로 전달할 수 있도록 다층기판 구조의 영상신호 전송 인터페이스를 분석하였다. 실제 설계한 PCB의 전원층의 형상의 구조와 크기, 배선의 위치 및 다층구조 PCB의 RLC소자들에 의해 물리적으로 발생하는 주파수 공진과 공진위치를 분석하여 노이즈에 취약한 주파수를 확인하였다. PCB 패턴 및 Via 설정, 디커플링 커패시터를 추가하여 공진특성의 변화를 모의 실험한 결과, V-by-One HS 인터페이스 다층기판의 전원층간 발생하는 공진이 크기가 감소하였다. 설계한 보드의 최초 공진 주파수가 200MHz 대역에서 발생하였으며, 디커플링 커패시터 추가 및 비아 홀을 추가 적용하여 공진 주파수를 제거시켰다. 최적화된 V-by-One HS 고속 영상신호 인터페이스 보드의 AC 커플링 커패시터를 100nF하여 전송선로 길이가 50mm 이하 일 때, Eye패턴 크기는 710mV, 지터는 3.735ps, 상승/하강 시간은 각각 3.491/ 3.539(ps)로 영상출력 신호가 가장 안정적으로 동작 하였고 실제 분석한 결과를 적용한 영상패턴 제어 신호발생기의 영상패턴 출력력이 V-by-One HS Eye 패턴 전송 품질규격을 만족 하였다. 향후, 8K4K Ultra-HD급 영상신호 V-by-One HS 인터페이스를 적용하여 초고해상도 8K-UHD TFT LCD 패널 검사 분야에 사용될 수 있으며 차량용 인포테인먼트 시스템과 시큐리티 등으로 다양한 분야에 응용할 수 있다.

## 참 고 문 헌 (References)

- [1] Kaneko, K., & Ohta, N., 4K applications beyond digital cinema, In Virtual Systems and Multimedia (VSMM), 2010 IEEE 16th International Conference on, pp. 133-136, October, 2010.

- [2] Yi-feng, H., & Zhao-wen, Y., The Simulation and Pre-design on the PCB of the Simulator, In 2008 Asia-Pacific Symposium on Electromagnetic Compatibility and 19th International Zurich Symposium on Electromagnetic Compatibility, pp. 871-874, 2008.

- [3] Jeon, H. K., Kim, H. R., Choi, J. M., Hong, J. P., Kim, Y. S., Oh, H. S., Kim, L. S., High speed serial interface for mobile LCD driver IC, In Circuits and Systems, ISCAS 2008 IEEE International Symposium on, pp. 157-160, May, 2008.

- [4] Takizuka, H., Torikai, T., Mitsui, A., Suzuki, H., Watanabe, Y., Toma, T., & Koike, Y., A proposal of novel optical interface to transmit 8K-UHDTV for consumer applications, 2013 IEEE 18th Micro Optics Conference (MOC), pp. 1-2, October, 2013.

- [5] Fu, L., Han, Y., & Wu, K., Signal integrity research for high-speed video system design based on HyperLynx simulation, In Computer Research and Development (ICCRD), 2011 3rd International Conference on, Vol. 3, pp. 15-18, March, 2011.

- [6] Lingambudi, A., Edlund, G., Haridass, A., & Becker, D., A case study of high-speed serial interface simulation with IBIS-AMI models, In Electrical Design of Advanced Packaging and Systems Symposium (EDAPS), pp. 145-148, December, 2012.

- [7] Chung, S. L., Chen, W. Y., Design of Test Pattern Databank for functional testing of LCD panels. In Industrial Electronics, 2006 IEEE International Symposium on, Vol. 4, pp. 3002-3007, July, 2006.

- [8] Duan, X., Rimolo-Donadio, R., Bruns, H., & Schuster, C., Fast and concurrent simulations for SI, PI, and EMI analysis of multilayer printed circuit boards, In Electromagnetic Compatibility (APEMC), 2010 Asia-Pacific Symposium on, pp. 614-617, April, 2010.

- [9] Xiong, Y., & Yan, Z., EMI and PI analysis of analog board, In Microwave, Antenna, Propagation and EMC Technologies for Wireless Communications (MAPE), 2013 IEEE 5th International Symposium on, pp. 171-175, October, 2013.

- [10] Li-Xin, W., Yu-xia, Z., & Gang, Z., Power Integrity Analysis for High-Speed PCB, In Pervasive Computing Signal Processing and Applications (PCSPA), 2010 First International Conference on, pp. 414-418, September, 2010

- [11] Shang, E. T. M., Chyan, L. S., & Sebastian, P., Signal integrity analysis for high speed digital circuit, In Intelligent and Advanced Systems (ICIAS), 2010 International Conference on, pp. 1-6, June, 2010.

- [12] Johnson, D., An FPGA-based solution for testing legacy video displays, In AUTOTESTCON, pp. 1-4, September, 2010

- [13] Cho, K., Lee, S. J., Kim, S. M., & Kim, D. H., Display signal interface techniques for mobile applications, In Quality Electronic Design (ASQED), 2011 3rd Asia Symposium on, pp. 105-108, July, 2011.

- [14] Brandl, A., Recht, E., & Bar-Natan, V., LVDS signal integrity for video transmission lines, In Electromagnetic Compatibility, 2003 IEEE International Symposium on, Vol. 1, pp. 537-538, May, 2003.

- [15] Park, W., & Lee, S. C., Design of LVDS driver based CMOS transmitter for a high speed serial link, In Electronics and Information Engineering (ICEIE), 2010 International Conference On, Vol. 1, pp. 300-302, August, 2010.

---

### 저 자 소 개

---

손 희 배

- 2009년 ~ 현재 : 경남대학교 대학원 첨단공학과 박사과정

- 2011년 ~ 현재 : (주)MIK21 책임연구원

- 주관심분야 : Ultra-HD, 영상신호처리, EMI/EMC

권 오 근

- 2007년 ~ 현재 : (주)MIK21 연구소장

- 주관심분야 : Ultra-HD, FPGA, 영상신호처리