특집논문 (Special Paper)

방송공학회논문지 제30권 제6호, 2025년 11월 (JBE Vol.30, No.6, November 2025)

<https://doi.org/10.5909/JBE.2025.30.6.1016>

ISSN 2287-9137 (Online) ISSN 1226-7953 (Print)

## 다중 표준 비디오 코덱을 위한 스케일러블 DCT-II 변환 모듈 설계

윤승환<sup>a)</sup>, 오수민<sup>a)</sup>, 이동윤<sup>a)</sup>, 성영재<sup>a)</sup>, 서영호<sup>a)†</sup>

## Scalable DCT-II Module Design for Multi-Standard Video Codecs

Seung-Hwan Yoon<sup>a)</sup>, Su-Min Oh<sup>a)</sup>, Dong-Yun Lee<sup>a)</sup>, Young-Jae Sung<sup>a)</sup>, and Young-Ho Seo<sup>a)†</sup>

### 요약

본 연구는 다중 표준 비디오 코덱(AVC, HEVC, VVC)의 DCT-II 기반 변환 모듈을 단일 하드웨어 구조로 통합하고, 연산 속도와 볼록 크기를 스케일러블하게 조절할 수 있는 통합 변환 모듈을 제안한다. 제안 구조는 열 단위 Shift & Adder Unit(SAU) 기반 행렬 곱과 Gray Code 입력 정렬을 활용하여 곱셈기를 제거하고 LUT와 레지스터 자원을 절감하며, 8K 60 FPS 실시간 처리를 550 MHz에서 달성한다. 또한, 상위 모듈의 메모리 대역폭 요구에 따라 처리량을 동적으로 조절할 수 있다. FPGA 환경에서 검증한 결과, 제안 구조는 기존 연구 대비 하드웨어 자원 효율성과 연산 성능에서 우수함을 확인하였다. 본 연구는 초고해상도 및 고프레임레이트 환경에서 효율적인 DCT-II 중심 하드웨어 기반 변환 모듈 설계 가능성을 제시한다.

### Abstract

This paper proposes a unified hardware transform module that integrates DCT-II - based transforms for multi-standard video codecs (AVC, HEVC, and VVC). The architecture allows scalable adjustment of processing speed and block size while removing multipliers through a column-wise Shift & Adder Unit (SAU) - based matrix multiplication and Gray-code input alignment. This approach significantly reduces LUT and register utilization and achieves real-time 8K 60 FPS operation at 550 MHz. Moreover, the proposed design dynamically adjusts throughput according to memory bandwidth requirements, enabling efficient adaptation to system constraints. FPGA implementation results verify that the proposed architecture outperforms previous designs in both hardware efficiency and computational performance. The study demonstrates the feasibility of an efficient, DCT-II - centric hardware transform architecture optimized for ultra-high-resolution and high-frame-rate video processing environments.

Keyword : Video Compression, Transform, DCT-II, Hardware Acceleration

a) 광운대학교 전자재료공학과(Department of Electronic Materials Engineering, Kwangwoon University)

† Corresponding Author : 서영호(Young-Ho Seo)

E-mail: yhseo@kw.ac.kr

Tel: +82-2-940-8362

ORCID: <https://orcid.org/0000-0003-1046-395X>

※ 이 논문의 결과 중 일부는 한국방송·미디어공학회 2025년 학제학술대회에서 발표한 바 있음

※ This work was supported by the National Research Foundation of Korea(NRF) grant funded by the Korea government(MSIT) (No. RS-2025-16071490)

· Manuscript September 23, 2025; Revised November 6, 2025; Accepted November 7, 2025.

## I. 서 론

최근 영상 서비스 시장은 초고해상도 및 고프레임레이트 콘텐츠의 수요 증가와 함께, 다양한 세대의 비디오 압축 표준이 공존하는 환경에 직면하고 있다. 특히, 기존 H.264/AVC, 차세대 H.265/HEVC, 최신 H.266/VVC와 같은 세대별 코덱은 방송, 스트리밍, 저장 장비 등 다양한 응용 환경에서 혼재되어 사용되고 있다. 이러한 상황에서 새로운 표준으로의 전환이 자연될 경우, 구세대와 신세대 코덱의 동시 운용은 필수적이며, 이에 따라 하드웨어 설계 및 유지보수 비용 증가라는 문제가 발생한다.

세대별 비디오 코덱은 서로 다른 표준 규격을 가지지만, 변환, 양자화, 예측 등 주요 알고리즘은 많은 부분에서 유사하거나 동일한 구조를 공유한다. 이로 인해 기존 연구에서는 다양한 크기와 타입의 변환 모듈을 단일 하드웨어 구조로 통합하여 자원 절감을 도모하는 접근이 다수 제안되어 왔다. 그러나 이러한 연구들은 대부분 정해진 변환 크기나 특정 표준 환경에 한정되어 있어, 실제 시스템의 동적 대역폭 요구나 처리량 변동에 대응하기 어렵다는 한계가 있다.

본 연구는 이러한 한계를 극복하기 위해, 변환 크기와 처리 속도를 스케일러블하게 조절할 수 있는 DCT-II 기반 통합 변환 모듈을 제안한다. 제안 구조는 상위 시스템의 메모리 대역폭 제약에 따라 병렬도 및 처리율을 조정할 수 있는 제어 메커니즘을 포함하며, 이를 통해 자원 효율성과 연산 성능 간의 균형을 최적화할 수 있다.

제안 구조는 방송, 스트리밍, VR/AR, 클라우드 게임 등과 같이 다양한 품질·대역폭 요구를 가지는 응용 환경에서 특히 강점을 가진다. 고성능 모드에서는 최대 병렬 처리를 활용하여 8K 60fps 수준의 실시간 성능을 제공하며, 모바일·엣지 환경에서는 연산 속도를 조절하여 메모리 접근 및 자원 사용량을 줄일 수 있다.

특히 주목할 점은, 기존 연구가 주로 특정 모듈의 연산 최적화에 집중한 반면, 본 논문은 모듈 차원의 최적화 기법을 넘어 전체 시스템 레벨에서의 동작까지 아우르는 설계를 제안한다는 점이다. 즉, 개별 하드웨어 블록의 효율성뿐 아니라, 상위 제어부와의 연동, 동적 자원 배분, 대역폭 제약 조건 하의 전체 파이프라인 동작을 함께 고려하였다. 이를 통해 제안 구조는 단순한 하드웨어 블록 설계가 아닌,

실제 응용 서비스 환경에서 실질적으로 활용 가능한 시스템 수준의 통합 해법을 제시한다.

정량적으로, 본 연구의 목표는 550 MHz 동작 환경에서 8K 해상도 60 FPS 실시간 처리를 지원하면서도, 기존 고정형 설계 대비 자원 사용량을 유의미하게 절감하는 것이다. 본 논문은 제안 구조의 설계 원리와 스케일러블 제어 방식, 전체 시스템 수준에서의 동작 메커니즘, 그리고 성능 검증 결과를 순차적으로 제시함으로써, 다중 표준 환경뿐만 아니라 동적 대역폭 제약 하에서도 효율적으로 동작 가능한 새로운 형태의 변환 모듈 및 시스템 설계 가능성을 제시한다.

## II. 관련 연구

비디오 압축 표준에서 변환 과정은 주파수 영역에서의 에너지 집중도를 높이고, 양자화 효율을 극대화하는 핵심 단계이다. 특히, H.264/AVC 이후의 대부분의 표준에서는 이산 코사인 변환(Discrete Cosine Transform, DCT)이 기본 변환 방식으로 채택되었으며, 그 중에서도 DCT-II가 대표적으로 사용된다. DCT-II는 직교성과 높은 에너지 압축 효율을 갖추고 있어, 표준화 과정에서 지속적으로 활용되어 왔다.

기존 하드웨어 기반 DCT-II 구현에서는 Butterfly 구조와 decomposition 방식을 활용하여 연산량을 줄이는 접근이 일반적이었다. Butterfly 구조는 변환 행렬을 계층적으로 분해하여 곱셈 연산의 복잡도를 낮추고, 병렬 처리를 통해 처리 속도를 향상시키는 방식으로, 고속 푸리에 변환(Fast Fourier Transform, FFT)의 계산 절차를 변형하여 적용한다. 또한 일부 연구에서는 Shift & Adder Unit(SAU)을 활용하여 곱셈기를 제거하거나 최소화함으로써, LUT(Look-Up Table)와 DSP 자원의 사용량을 크게 줄이는 방법이 제안되었다. 이러한 접근은 FPGA와 같은 제한된 하드웨어 환경에서 특히 유용하며, 전력 소모와 칩 면적 절감에도 기여한다.

그러나 기존 연구들은 대부분 특정 표준이나 고정된 변환 크기에 특화되어 설계되었기 때문에, 다양한 표준과 변환 크기를 지원해야 하는 다중 표준 환경에서는 하드웨어

구조의 재설계가 필요하다는 한계가 존재한다. 따라서 변환 모듈의 범용성과 확장성을 동시에 확보할 수 있는 연구가 지속적으로 요구된다.

Fan et al.<sup>[1]</sup>은 VVC 표준의 다양한 블록 크기( $4\times 4$ ,  $8\times 8$ ,  $16\times 16$ ,  $32\times 32$ )와 변환 타입(DST-VII, DCT-VIII)을 지원하는 파이프라인 기반 고속 2D 변환 아키텍처를 제안하였다. 이 아키텍처는 N차원 최소 덧셈 그래프(N-Dimensional Reduced Adder Graph, RAG-n)를 적용하여 연산 단위를 최소화하고, 덧셈과 시프트 기반 연산을 활용하여 곱셈기를 제거함으로써 하드웨어 자원 효율을 높였다. 또한, 듀얼 포트 SRAM 기반 전치 메모리를 적용하여 데이터 접근 효율을 향상시키고, 최대 32 샘플/cycle 처리율을 달성하였다. Fan et al.의 연구는 다양한 블록 크기와 변환 타입을 지원하는 범용 2D 변환 아키텍처 설계 가능성을 제시하며, 실시간 4K 이상 영상 처리 환경에서 적합한 처리량과 전력 효율을 확보하였다.

Garrido et al.<sup>[2]</sup>은 VVC 표준 기반 다중 변환 프로세서를 설계하여 DCT-II, DCT-VIII, DST-VII 변환 유형을 모두 지원하면서  $4\times 4$ 부터  $32\times 32$ 까지 다양한 블록 크기를 처리할 수 있도록 하였다. FPGA 기반 구현을 통해 최대 4K 해상도에서 실시간 처리 성능을 달성했으며, 하드웨어 자원의 효율적 사용과 블록 크기 및 변환 타입 선택 기능을 동시에 제공하였다. 이 연구는 다중 변환 선택(Multiple Transform Selection, MTS) 기능을 지원하는 범용 하드웨어 설계 가능성을 보여주며, VVC 표준 기반 하드웨어 구현 연구의 중요한 기초를 제공한다.

Mert et al.<sup>[3]</sup>은 미래 비디오 코딩 표준을 위한 고성능 2D 변환 하드웨어를 제안하였다. 본 연구에서는 다양한 블록 크기와 변환 타입을 유연하게 지원할 수 있는 구조를 설계하고, Butterfly 기반 분해와 병렬 연산을 통해 높은 처리 속도를 달성하였다. FPGA 환경에서 최대 4K 해상도까지 실시간 처리가 가능하도록 설계되었으며, 곱셈기 사용을 최소화하여 하드웨어 자원 효율을 확보하였다. 또한, 변환 크기 확장성과 모듈 재사용성을 고려한 구조 설계를 통해 기존 고정형 변환 모듈의 한계를 극복하였다.

Kammoun et al.<sup>[4]</sup>은 Adaptive Multiple Transform(AMT) 기반 하드웨어 구조를 제안하였다. 이 연구에서는 다양한 블록 크기와 변환 타입을 지원할 수 있는 유연한 구조를

제공하며, ASIC 및 FPGA 환경 모두에서 구현 가능하다. AMT 기반 설계는 변환 블록 크기와 선택된 변환 타입에 따라 하드웨어 처리 유닛을 동적으로 조절할 수 있어, 실시간 처리 성능을 유지하면서 하드웨어 자원 활용을 최적화 한다. 또한, 메모리 접근과 처리 유닛 배치를 조정하여 전력 소모를 줄이는 방안이 포함되어 있어, 모바일 및 저전력 환경에서도 효율적이다.

Farhat et al.<sup>[5]</sup>은 경량 VVC 변환 블록을 ASIC 기반으로 구현하여 실시간 4K 디코딩 성능을 달성하였다. 본 연구에서는 곱셈기를 제거하고 LUT 기반 최적화를 적용하여 하드웨어 자원을 절감하였으며, 전력 효율 향상에도 기여하였다. 특히, 제한된 리소스 환경에서 고해상도 VVC 변환을 구현할 수 있음을 보여주어, 저전력 고효율 하드웨어 설계 가능성을 확인하였다.

종합하면, 기존 연구들은 대부분 특정 표준이나 고정된 변환 크기에 맞춘 설계가 중심이었으며, 다중 표준 환경과 다양한 블록 크기를 지원하는 범용 하드웨어 설계의 필요성이 지속적으로 제기되어 왔다. 실시간 고해상도 영상 처리 환경에서는 단순히 기능을 통합하는 것만으로는 하드웨어 자원 활용을 극대화할 수 없으며, 처리량과 메모리 대역폭 제약을 동시에 고려한 설계가 요구된다. 이러한 요구사항을 충족하기 위해서는, 파이프라인 처리 구조, 연산 단위 최적화, 동적 블록 크기 지원, 메모리 접근 효율화 등을 종합적으로 고려한 통합 변환 모듈 설계가 필요하다.

이에 반해, 본 연구는 기존의 모듈 단위 최적화를 넘어 시스템 수준의 자원 제어 및 동적 처리율 조절 메커니즘을 통합적으로 고려한 설계를 제안한다. 즉, 동적 대역폭 대응과 실시간 자원 최적화를 동시에 만족하는 구조를 통해, 기존 연구 대비 확장성·유연성·자원 효율성 측면에서 차별성을 가진다.

### III. 하드웨어 구조

본 절에서는 다중 표준 비디오 코덱의 변환 모듈을 단일 하드웨어 구조로 통합하기 위해, 연산 효율과 하드웨어 자원 절감을 동시에 달성할 수 있는 DCT-II 하드웨어 최적화 기법을 제안한다. 기존 하드웨어 기반 DCT-II 구현은 표준

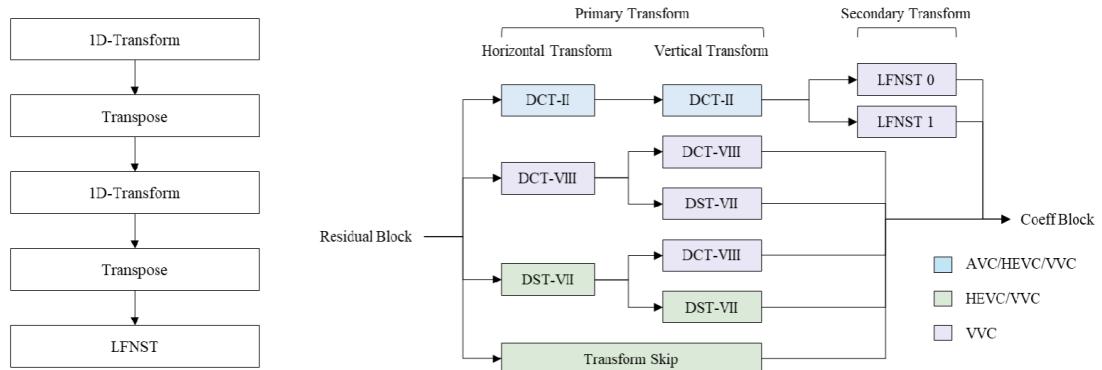

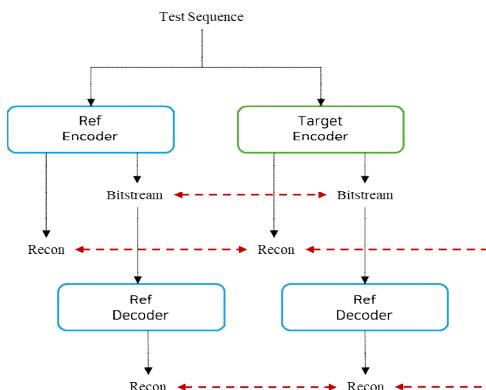

그림 1. 코데별 reference software의 동작 흐름

Fig. 1. Operation flow of reference software by codec

별로 고정된 변환 크기와 구조에 맞추어 설계되는 경우가 많아, 변환 크기 확장성과 모듈 재사용성이 제한되는 문제가 있다. 또한, 곱셈기 기반의 연산 구조는 FPGA 및 ASIC 환경에서 높은 자원 소모와 전력 소모를 유발한다. 이러한 문제를 해결하기 위해, 본 연구에서는 DCT 변환 모듈의 구조화와 열단위 SAU 기반의 행렬곱 처리 방법을 제안하고, DCT-II 변환 모듈의 하드웨어 구조를 제안한다.

## 1. 통합 변환 모듈의 구조화

제안하는 첫 번째 솔루션은 AVC/HEVC/VVC를 통합하는 변환 모듈의 구조화이다. 표준 비디오 코덱의 2차원 변환(2D Transform)은 일반적으로 두 번의 1차원 변환(1D Transform)과 두 번의 전치 연산(Transpose), 그리고 추가적인 2차 변환으로 구성된다. 이러한 변환 구조는 AVC, HEVC, VVC 등 주요 표준에서 공통적으로 사용된다<sup>[6]</sup>. 이를 기반으로 본 연구에서는 하드웨어 구현 시에도 동일한 처리 흐름을 반영하여 모듈 단위로 구성하였다. 특히, 수평 변환과 수직 변환은 연산 구조는 동일하지만, 입력 데이터의 비트 범위가 서로 다르므로 각각 독립된 모듈로 설계하였다. 이를 통해 변환 방향에 따른 파이프라인 최적화가 가능하며, 높은 동작 주파수를 유지할 수 있다.

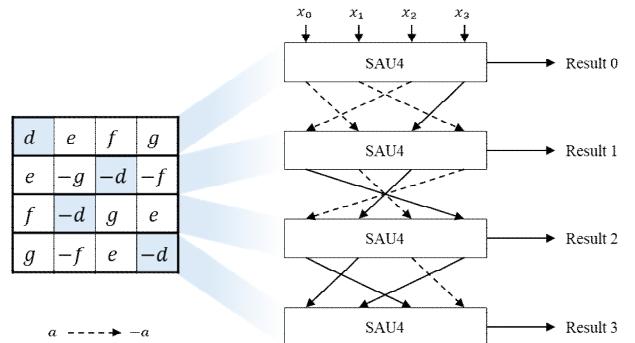

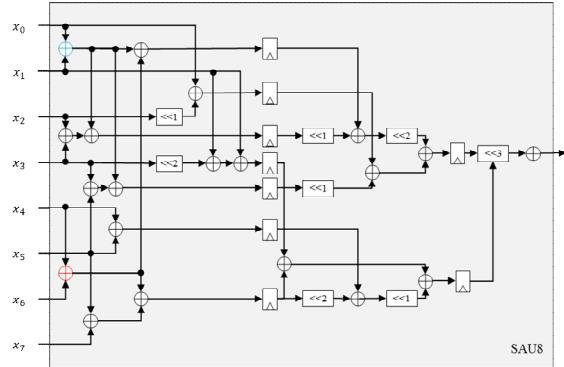

## 2. 열단위 SAU 기반 행렬곱

두 번째 솔루션은 전체 DCT-II 행렬곱을 열 단위 SAU로

처리하는 구조이다. SAU는 곱셈기를 사용하지 않고, 상수 계수를 시프트와 덧셈 연산만으로 구현하는 연산기로, 고정 계수 연산에 최적화되어 있다. DCT-II 행렬의 각 열은 동일한 계수가 고정된 형태로 한 번씩만 등장하며, 위치만 바뀌는 특성을 가진다. 이러한 특성을 활용하면 입력 데이터를 재배치하여 동일한 SAU 구조를 반복적으로 사용할 수 있다.

그림 2. SAU4와 입력 재배치를 이용한 행렬곱 구현 구조

Fig. 2. Matrix Multiplication Implementation Using SAU4 and Input Reordering

이를 통해 전체 행렬곱을 동시에 계산하는 대신<sup>[7]</sup>, 출력 데이터 전송 속도에 맞춰 스케일러블하게 처리할 수 있으며, 곱셈기를 완전히 제거하여 하드웨어 자원을 절감할 수 있다. 추가적으로, 곱셈 계수를 인수분해하여 SAU의 연산 경로를 단순화하였으며, 이 과정에서 Gray Code 기반 입력 정렬 최적화를 적용하였다. Gray Code는 인접한 수의 비트

| Template | Value | Graycode | Binary        |

|----------|-------|----------|---------------|

| I        | 87    | 124      | 1 0 1 0 1 1   |

| J        | 80    | 120      | 1 0 1 0 0 0 0 |

| H        | 90    | 119      | 1 0 1 1 0 1 0 |

| K        | 70    | 101      | 1 0 0 0 1 1 0 |

| M        | 43    | 62       | 0 1 0 1 0 1 1 |

| L        | 57    | 37       | 0 1 1 1 0 0 1 |

| N        | 25    | 21       | 0 0 1 1 0 0 1 |

| O        | 9     | 13       | 0 0 0 1 0 0 1 |

그림 3. Gray Code 정렬을 활용한 Adder Tree 최적화 예시

Fig. 3. Example of Adder Tree Optimization Using Gray Code Ordering

표 1. Adder Tree 최적화의 효율 분석

Table 1. Efficiency of Adder Tree Optimization

|       | Baseline   | Ours      | Reduced Adder |

|-------|------------|-----------|---------------|

| SAU8  | 27 Adders  | 24 Adders | -3 Adders     |

| SAU16 | 56 Adders  | 43 Adders | -13 Adders    |

| SAU32 | 107 Adders | 86 Adders | -21 Adders    |

차이가 1이 되도록 설계되어 있어, 인접한 연산 간 중복 처리를 줄이고 불필요한 덧셈기 사용을 감소시킬 수 있다. 표 1의 결과처럼 기존 방식 대비 평균 약 20%의 연산기 감소 효과를 얻었다.

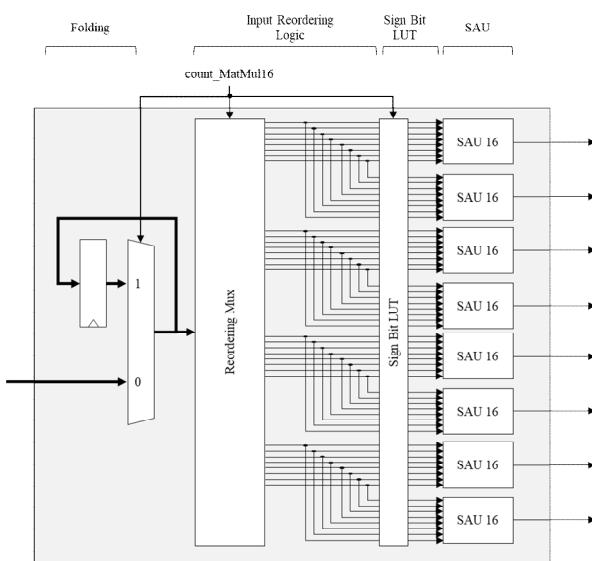

그림 4. Matmul16의 블록도

Fig. 4. Block Diagram of Matmul16

열단위 SAU 기반 행렬곱 구조는 다음 두 부분으로 구성된다.

- SAU - 고정 계수를 시프트 및 덧셈 연산만으로 구현하여 곱셈기를 제거

- Input Reordering Logic - 입력 데이터를 미리 재배치하여 SAU 구조를 단순화하고, 계수 대칭성을 활용하여 하드웨어 복잡도를 절감

특히 DCT-II 계수의 점대칭 특성을 이용해 상위 절반의 입력 재배치 로직만 설계하고, 하위 절반은 반전하여 재사용하였다. 다만, 계수 부호의 대칭성이 완벽하지 않은 경우 삼각함수 계수 부호를 LUT로 구현하여 처리하였다.

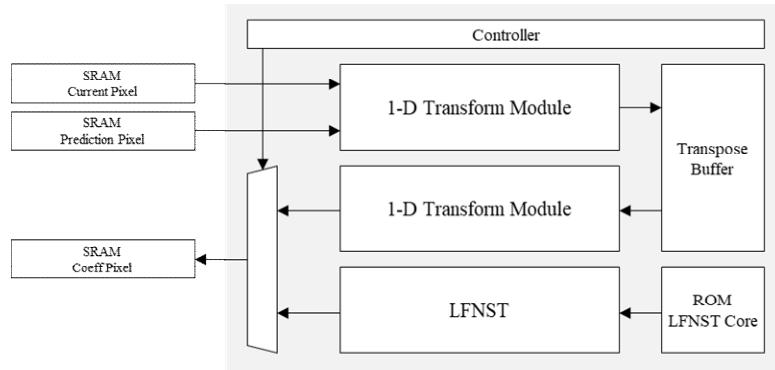

### 3. 통합 변환 모듈의 구조

본 연구에서 제안하는 통합 변환 모듈의 Top Architecture는 크게 두 개의 1-D Transform 모듈, 하나의 Transpose Buffer, 그리고 하나의 LFNST(Low-Frequency Non-Separable Transform) 모듈로 구성된다. 이 구조에서 SRAM은 원본 영상 데이터를 저장하는 Current Pixel, Intra/Inter Predictor로부터 생성된 예측 영상 데이터를 저장하는 Prediction Pixel, 그리고 변환된 계수 데이터를 저장하는 Coeff Pixel로 구분하여 운용된다. 모듈 구성은 1-D Transform Module과 Secondary Transform을 수행하는 LFNST 모듈로 이루어져 있으며, 2차원 변환 과정에서 필요한 데이터 전치를 위해 Transpose Buffer를 포함한다. 또한 LFNST 모듈에서

그림 5. 통합 변환 모듈의 블록도

Fig. 5. Block Diagram of Unified Transform Module

사용할 가중치는 전용 ROM에 저장된 LFNST Core에서 제공된다. 단 본 논문은 1-D Transform Module 중 DCT-II 모듈에 한해 설계한다.

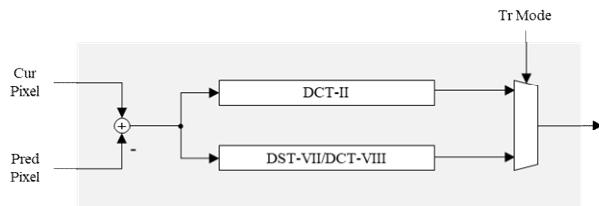

그림 6. 1-D Transform Module의 블록도

Fig. 6. Block Diagram of 1-D Transform Module

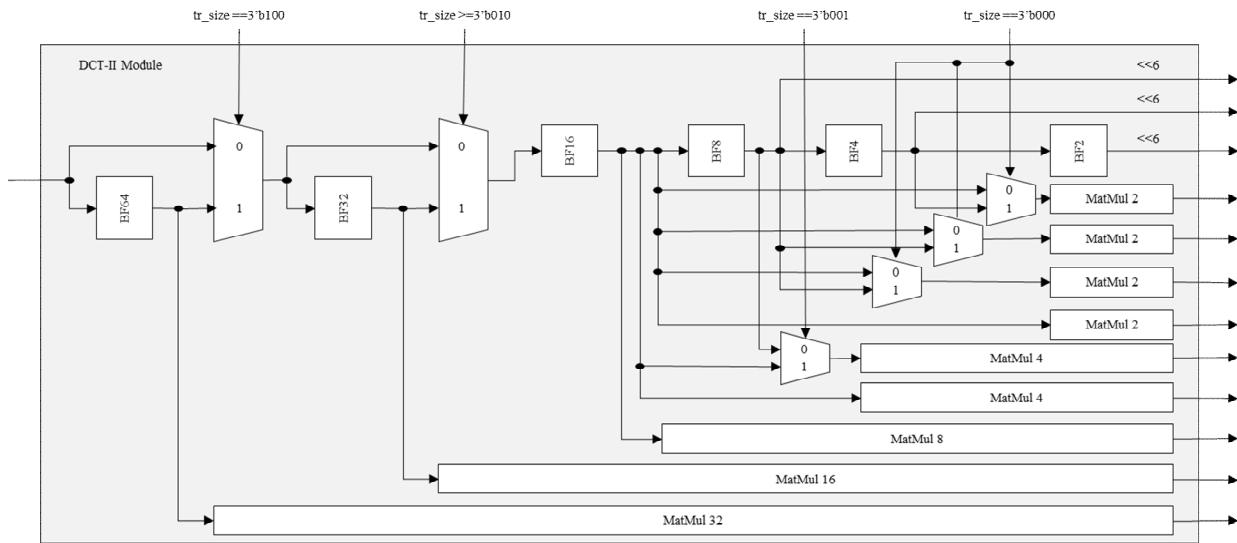

#### 4. DCT-II 모듈의 구조

DCT-II 모듈은 8K 해상도에서 60 FPS 이상을 처리할 수 있도록 550 MHz 동작 주파수 환경에서 16 Pixel/cycle 처리 성능을 목표로 한다. 기본 구조는 전통적인 버터플라이 기반 설계를 따르지만, 입출력 속도를 유연하게 조절하기

위해 MatMul 유닛을 병렬로 배치하고 입력 샘플 수에 따라 입력 위치를 조정하는 컨트롤 로직을 추가하였다. 또한, 1 cycle당 출력이 1column 미만일 경우 folding register를 통해 입력 데이터를 저장 후 다음 cycle에서 재활용하도록 하였으며, 각 열에 해당하는 입력 순서를 재배치하기 위해 Input Reordering Logic을 적용하였다. 계수 위치에 따른 부호 변화는 Sign Bit LUT로 처리하고, 곱셈 연산은 곱셈기 대신 고정 계수에 최적화된 SAU를 사용하여 Shift와 Add만으로 수행하였다. SAU의 최소 개수는 입력 샘플 수에 기반하여 결정하며, 자원 활용과 성능의 균형을 위해 8개 단위로 병렬 배치하였다. 이러한 구조는 곱셈기 기반 설계 대비 FPGA의 LUT와 DSP 자원을 크게 절감하면서도 동일한 클록 주파수에서 높은 처리량을 제공한다.

그림 7은 표 2의 연산 모듈 배치 결과를 기반으로 구성된 전체 블록도를 나타낸다. 입력 데이터의 샘플 수에 따라 사이클당 처리되는 컬럼 수가 달라지며, 이에 따라 활성화되는 MatMul 유닛의 구성이 동적으로 조정된다. 사이클당 1 컬럼 이하로 연산되는 경우(64, 32, 16 샘플 입력)에는

표 2. 고정된 연산 속도 환경에서 입력 샘플 수 별 최적의 연산 모듈 배치

Table 2. Optimal computational module placement by number of input samples in a fixed computational speed environment

|            | SAU2 | SAU4 | SAU8 | SAU16 | SAU32 | Operation Speed |

|------------|------|------|------|-------|-------|-----------------|

| 4 Samples  | 8    | -    | -    | -     | -     | 4 Col/Cycle     |

| 8 Samples  | 4    | 8    | -    | -     | -     | 2 Col/Cycle     |

| 16 Samples | 2    | 4    | 8    | -     | -     | 1 Col/Cycle     |

| 32 Samples | 1    | 2    | 4    | 8     | -     | 0.5 Col/Cycle   |

| 64 Samples | 0.5  | 1    | 2    | 4     | 8     | 0.25 Col/Cycle  |

그림 7. DCT-II Module의 블록도

Fig. 7. Block Diagram of DCT-II Module

MUX 제어 신호에 의해 각각 MatMul32, MatMul16, MatMul8, MatMul4, MatMul2 유닛이 각각 한 개씩 활성화된다. 반면, 사이클당 2컬럼 처리가 필요한 8 샘플 입력의 경우 MatMul4 및 MatMul2 유닛이 각각 두 개씩 활성화되며, 사이클당 4컬럼 처리가 요구되는 4 샘플 입력에서는 MatMul2 유닛 네 개가 병렬로 활성화된다. 따라서 전체 구성은 MatMul32, MatMul16, MatMul8 유닛 각 1개, MatMul4 유닛 2개, MatMul2 유닛 4개로 구성된다.

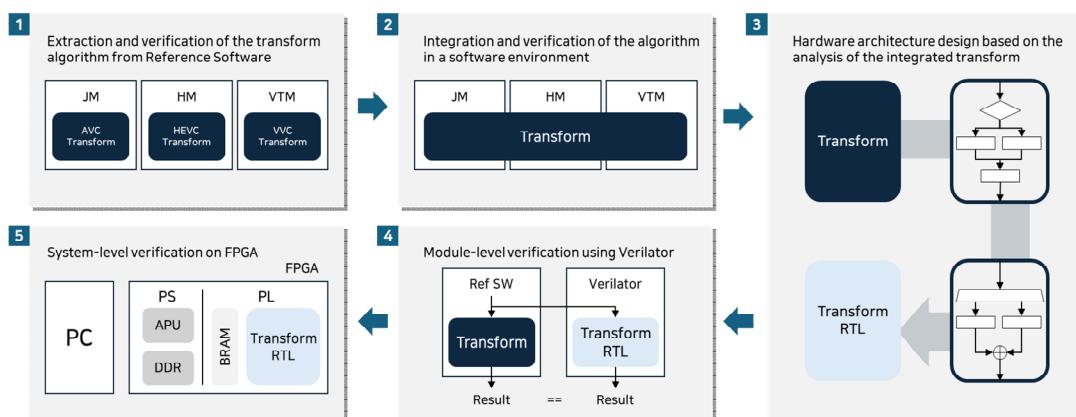

#### IV. 실험 및 구현결과

본 연구에서는 다중 표준 비디오 코덱의 변환 기능을 단일 하드웨어 구조로 통합 구현함에 있어, 제안 모듈의 기능적 정확성과 하드웨어 구현 가능성을 체계적으로 검증하기 위한 소프트웨어-하드웨어 통합 검증 환경을 구축하였다. 평가 과정은 다음과 같은 5단계로 구성된다. 이와 같은 단계별 검증 절차를 통해 정확성, 호환성, 그리고 하드웨어

그림 8. 제안하는 통합 변환 모듈의 소프트웨어 - 하드웨어 검증 흐름

Fig. 8. Software - Hardware Verification Flow of the Proposed Unified Transform Module

효율성을 종합적으로 평가하였다.

#### 1. 변환 모듈의 독립 추출 및 재구성 결과

각 표준 코덱의 reference software에서 변환 모듈을 객체 지향적으로 분석하여 해당 기능만을 독립적으로 추출하고, 이를 재구성하여 동일성을 검증하였다. 이를 통해 표준 규격별 변환 연산의 기본 동작을 확인하였다.

## 2. 소프트웨어 통합 검증 결과

본 연구에서는 3개의 주요 코덱(AVC, HEVC, VVC)의 변환 모듈을 소프트웨어 환경에서 통합 구현한 후, 이를 각 코덱의 reference software 인코더에 삽입하여 통합 모듈의 정확성을 검증하였다. 검증 절차는 다음과 같다.

- 시험 영상을 reference software와 제안 인코더를 통해 각각 압축한 뒤, 생성된 비트스트림 간의 동일성 확인

- reference software 인코더에서 출력된 복원 영상과 제안 인코더에서 출력된 복원 영상을 비교하여 동일성 검증

- 각 비트스트림을 reference software 디코더로 복원한 후, 최종 복원 영상의 동일성 검증

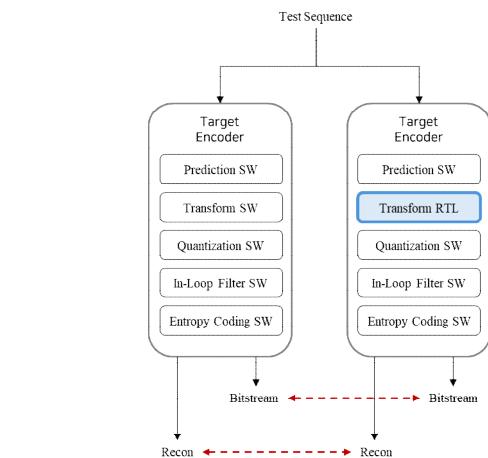

### 3. 하드웨어 RTL 구현 결과

소프트웨어 검증을 통해 기능이 확정된 통합 변환 모듈의 구조를 분석하여, 이를 하드웨어 RTL(Register Transfer Level)으로 구현하는 과정입니다.

Level)로 설계 및 구현하였다.

본 연구에서는 다중 표준 비디오 코덱의 변환 모듈을 단일 구조로 통합함과 동시에, 다양한 변환 블록 크기에 대해 연산 속도를 확장 가능하게 조절할 수 있는 구조를 제안하였다. 제안된 통합 변환 모듈은 단순히 기능을 통합하는 수준을 넘어, 상위 모듈에서 요구하는 메모리 대역폭에 맞추어 처리량을 세부적으로 조절할 수 있도록 설계되었다. 이를 통해 하드웨어 자원 활용도를 극대화하고, 새로운 표준 확장 시에도 유연한 대응이 가능함을 확인하였다.

FPGA 환경에서 합성 및 성능 검증을 수행한 결과, 기존 연구들과 공정 기술, 클럭 속도, 해상도, 지원 모드가 상이하여 직접적인 비교는 제한적이었다. 이러한 한계를 극복하기 위해 본 논문에서는 새로운 효율 지표  $\theta$ 를 도입하였다.  $\theta$ 는 연산 능력(Pixel per Cycle) 대비 하드웨어 자원 소모량으로 정의되며, 다음과 같이 나타낼 수 있다.

**Transform** 연산은 모든 열을 병렬화함으로써 매우 짧은 클록 주기로 처리할 수 있다. 그러나 병렬화 수준을 두 배로 늘리면 처리 속도는 약 두 배 향상되지만, 동시에 하드웨어 면적 또한 두 배 증가한다. 즉, 단순한 병렬화 확장은 절대적인 성능 향상에는 기여하지만, 자원 효율성 측면에서는 비례적인 이득을 제공하지 못한다. 따라서 본 연구에서는 연산 속도와 하드웨어 자원 소모량 간의 균형을 공정하게 비교하기 위해, Pixel per Cycle 대비 자원 사용량을 기반으로 하는 효율 지표를 정의하였다. 이러한 지표는 병렬화 수준이나 클록 속도의 차이에 관계없이, 동일한 기준에서 하드웨어 효율성을 평가할 수 있는 합리적인 척도로 작용한다.

표 3. 다양한 하드웨어 기반 영상 변환 솔루션 성능 및 기술 비교

Table 3. Comparison of Hardware-Based Video Transform Solutions Across Studies

표 4. FPGA 기반 영상 변환 하드웨어 자원 및 연산 효율 비교

Table 4. Comparison of Hardware Resource Usage and Computational Efficiency for FPGA-Based Video Transforms

| Solutions                  | Garrido et al. <sup>[2]</sup> | Kammoun et al. <sup>[4]</sup> | Farhat et al. <sup>[5]</sup> | Ours             |

|----------------------------|-------------------------------|-------------------------------|------------------------------|------------------|

| Estimated LUTs             | 1968                          | 199525                        | 21552                        | 29628            |

| DSPs                       | 32                            | 1561                          | 32                           | 0                |

| Registers                  | 3624                          | -                             | 14368                        | 17752            |

| Pixel per Cycle            | 0.4158772                     | 0.705306                      | 0.628364                     | 3.619375         |

| $\theta_{LUTs} \downarrow$ | 4732.1659                     | 282892.1                      | 34298.61                     | 8185.945         |

| $\theta_{Reg} \downarrow$  | 8714.1103                     | -                             | 22865.74                     | 4904.715         |

| Transform Size             | 4, 8, 16, 32                  | 4, 8, 16, 32                  | 4, 8, 16, 32, 64             | 4, 8, 16, 32, 64 |

| Transform Type             | DCT-II/VIII<br>DST-VII        | DCT-II/VIII<br>DST-VII        | DCT-II/VIII<br>DST-VII       | DCT-II           |

$$\theta_{LUTs} = \frac{\text{Estimated LUTs}}{\text{pixel/cycle}}$$

$$\theta_{Reg} = \frac{\text{Reg}}{\text{pixel/cycle}}$$

여기서 ALMs는 1.5 LUTs로 환산하여 계산하였다. 제안된 지표를 활용한 비교 결과, 본 연구의 구조는 Register 효율 ( $\theta_{Reg}$ ) 측면에서 가장 우수하였으며, LUT 효율 ( $\theta_{LUTs}$ ) 역시 두 번째로 좋은 성능을 보였다. 또한 Pixel per Cycle 측면에서는 기존 연구 대비 우수한 연산 능력을 달성하였다.

#### 4. Verilator 기반 소프트웨어-하드웨어 동등성 검증 결과

구현된 하드웨어 RTL을 Verilator를 통해 C++ 시뮬레이션 환경에서 실행하고, 초기 소프트웨어 모델과의 출력 동일성을 비교하여 기능적 일치 여부를 확인하였다.

그림 9. 타겟 인코더의 소프트웨어적 검증

Fig. 9. Software Verification for the Target Encoder

그림 10. 타겟 인코더의 Verilator 검증

Fig. 10. Verification Environment Using Verilator for the Target Encoder

#### V. 결 론

최종적으로, 제안된 구조는 550 MHz 동작 주파수에서 8K 해상도 영상을 60 FPS 이상 처리할 수 있는 성능을 확보하였다. 이는 단순한 변환 모듈 통합을 넘어, 메모리 대역폭 요구사항에 따른 처리량 조절 기능을 통해 하드웨어 자원 효율을 극대화한 결과이다. 따라서 본 연구는 향후 차세대 비디오 코덱의 실시간 고해상도 인코딩 환경에서 효율적인 하드웨어 구현 방안을 제시할 수 있을 것으로 기대된다.

다만, 본 연구에서는 FPGA 환경을 기반으로 연산 효율성과 자원 활용도를 중심으로 성능을 검증하였기 때문에, 실제 ASIC 구현 시 공정 기술 및 전력 특성에 따른 추가적

인 최적화 연구가 필요하다. 또한 본 논문에서 제안한 구조는 DCT-II 중심으로 설계되어 있어, DST-VII 및 DCT-VIII과 같은 기타 변환 타입에 대한 지원은 향후 연구 과제로 남아 있다. 추후 연구에서는 전력 소모 및 발열 특성 분석을 포함한 종합적인 하드웨어 효율성 평가와, 다중 변환 타입을 동적으로 지원할 수 있는 확장형 구조로의 발전을 목표로 할 예정이다.

### 참 고 문 헌 (References)

- [1] Y. Fan, Y. Zeng, H. Sun, J. Katto, and X. Zeng, “A pipelined 2D transform architecture supporting mixed block sizes for the VVC standard,” IEEE Transactions on Circuits and Systems for Video Technology, Vol.30, No.9, pp.3289-3295, Sept. 2020.

doi: <https://doi.org/10.1109/TCSVT.2019.2934752>

- [2] M. J. Garrido, F. Pescador, M. Chavarriás, P. J. Lobo, and C. Sanz, “A 2-D multiple transform processor for the versatile video coding standard,” IEEE Transactions on Consumer Electronics, Vol.65, No.3, pp.274-283, Aug. 2019.

doi: <https://doi.org/10.1109/TCE.2019.2913327>

- [3] A. C. Mert, E. Kalali, and I. Hamzaoglu, “High performance 2D transform hardware for future video coding,” IEEE Transactions on Consumer Electronics, Vol.62, No.2, pp.178-186, May 2017.

doi: <https://doi.org/10.1109/TCE.2017.014862>

- [4] A. Kammoun, W. Hamidouche, F. Belghith, J. Nezan, and N. Masmoudi, “Hardware design and implementation of adaptive multiple transforms for the versatile video coding standard,” IEEE Transactions on Consumer Electronics, Vol.64, No.4, pp.412-420, Oct. 2018.

doi: <https://doi.org/10.1109/TCE.2018.2875528>

- [5] I. Farhat, H. Hamidouche, J. Nezan, and M. Cagnazzo, “Lightweight hardware implementation of VVC transform block for ASIC decoder,” Proceedings of IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), Barcelona, Spain, pp.4327-4331, May 2020.

doi: <https://doi.org/10.1109/ICASSP40776.2020.9054281>

- [6] X. Zhao, J. Chen, Y. Ye, M. Karczewicz, and S. Liu, “Transform coding in the VVC standard,” IEEE Transactions on Circuits and Systems for Video Technology, Vol. 31, No. 10, pp. 3878-3890, Oct. 2021.

doi: <https://doi.org/10.1109/TCSVT.2021.3087706>

- [7] B. Farhat, Efficient Hardware Designs of the New Versatile Video Coding (VVC) Tools for ASIC Platforms, Ph.D. Dissertation, INSA de Rennes, Rennes, France, 2022.

---

### 저 자 소 개

---

#### 윤 승 환

- 2025년 2월 : 광운대학교 전자재료공학과 졸업(공학사)

- 2025년 3월 ~ 현재 : 광운대학교 전자재료공학과 일반대학원(석사과정)

- ORCID : <https://orcid.org/0009-0004-2066-6376>

- 주관심분야 : 하드웨어 설계, 딥러닝, 영상 코덱

#### 오 수 민

- 2025년 2월 : 광운대학교 전자재료공학과 졸업(공학사)

- 2025년 3월 ~ 현재 : 광운대학교 전자재료공학과 일반대학원(석사과정)

- ORCID : <https://orcid.org/0009-0008-9583-5399>

- 주관심분야 : 하드웨어 설계, 딥러닝, 영상 코덱

---

저자소개

---

이동윤

- 2022년 8월 : 광운대학교 전기공학과 졸업(공학사)

- 2025년 3월 ~ 현재 : 광운대학교 전자재료공학과 일반대학원(석사과정)

- ORCID : <https://orcid.org/0009-0001-2221-8479>

- 주관심분야 : 영상처리 및 압축

성영재

- 2025년 2월 : 한성대학교 기계전자공학부 졸업(공학사)

- 2025년 3월 ~ 현재 : 광운대학교 전자재료공학과 일반대학원(석사과정)

- ORCID : <https://orcid.org/0009-0008-4437-1029>

- 주관심분야 : 영상처리 및 압축, RTL 설계, NPU 하드웨어 설계

서영호

- 1999년 2월 : 광운대학교 전자재료공학과 졸업(공학사)

- 2001년 2월 : 광운대학교 일반대학원 졸업(공학석사)

- 2004년 8월 : 광운대학교 일반대학원 졸업(공학박사)

- 2005년 9월 ~ 2008년 2월 : 한성대학교 조교수

- 2008년 3월 ~ 현재 : 광운대학교 전자재료공학과 교수

- ORCID : <https://orcid.org/0000-0003-1046-395X>

- 주관심분야 : 실감미디어, 2D/3D 영상 신호처리, SoC 설계, 디지털 홀로그램